Superkleine 3D-transistor met nieuwe etstechniek: 2,5 nm!

13 december 2018

op

op

Onderzoekers van het MIT en de University of Colorado presenteren een 3D-Transistor, die minder dan half zo groot is als de kleinste huidige typen. De basis is een heel nieuwe microfabricagetechniek, die halfgeleiders atoom voor atoom modificeert.

Onderzoekers vinden altijd weer nieuwe manieren om het einde van de Wet van Moore (een verdubbeling van het aantal transistoren in een IC elke twee jaar) nog wat verder vooruit te schuiven. Als het horizontaal niet meer lukt, bouwen ze gewoon omhoog. De nieuwste 3D-transistors hebben nog maar een structuurbreedte van 7 nm. Daar passen er miljarden van op een chip met de oppervlakte van een nagel.

Op de IEEE International Electron Devices-meeting hebben onderzoekers een geheel nieuwe chemische etstechniek gepresenteerd onder de naam Thermal Atomic Level Etching (Thermal ALE ), waarmee halfgeleiders op atomaire schaal kunnen worden bewerkt. Daarmee zijn 3D-transistors met een breedte van maar 2,5 nm te fabriceren, die ook nog eens weinig energie nodig hebben.

Er zijn al wel „atomaire“ etstechnieken, maar dit nieuwe proces is nauwkeurig en levert betere transistors op. Verder worden gangbare fabricagetechnieken voor het opdampen van atoomlagen op substraten gebruikt, wat de nieuwe techniek gemakkelijk te integreren maakt in bestaande fabricagetechnieken.

Termisch ALE , zoals de University of Colorado het toepast, werkt met een chemische reactie die „ligandenuitwisseling“ wordt genoemd. Bij dit proces wordt een ion vervangen door een ligande van een andere verbinding. Bij het verwijderen van de chemicaliën worden met de liganden individuele atomen van de oppervlakte meeverwijderd. Tot nu toe werd deze techniek alleen gebruikt bij het etsen van oxiden.

De onderzoekers hebben thermisch ALE gemodificeerd voor halfgeleidermateriaal en werken met dezelfde reactor, die tot nu toe gereserveerd was voor ALD. Er is gebruik gemaakt van het gelegeerde halfgeleidermateriaal InGaAs (indium-gallium-arsenide), dat meer en meer wordt beschouwd als een beter alternatief voor silicium. Met fluorwaterstof wordt een laag metaalfluoride-moleculen gevormd op de oppervlakte. Dan wordt het materiaal bevochtigd met DMAC (dimethylaluminiumchloride). Bij het verwijderen van het DMAC worden individuele atomen meeverwijderd. Dit wordt honderden cycli lang herhaaldelijk gedaan. In een aparte reactor plaatsen de onderzoekers dan de gates van de transistoren.

Bij experimenten waren zo lagen van maar 0,02 nm dik te verwijderen zoals bij het afpellen van een ui. Dat maakt een enorm nauwkeurig etsproces mogelijk. En omdat deze techniek lijkt op die van ALD, kunnen hij plaatsvinden in dezelfde reactor die wordt gebruikt voor de depositie.

De nieuwe techniek levert een winst van ca. 60 % op in de transconductantie vergeleken met gewone FinFET’s. De transconductantie bepaalt hoeveel energie er nodig is aan de gate om de transistor te laten omschakelen.

Bron: MIT News

Onderzoekers vinden altijd weer nieuwe manieren om het einde van de Wet van Moore (een verdubbeling van het aantal transistoren in een IC elke twee jaar) nog wat verder vooruit te schuiven. Als het horizontaal niet meer lukt, bouwen ze gewoon omhoog. De nieuwste 3D-transistors hebben nog maar een structuurbreedte van 7 nm. Daar passen er miljarden van op een chip met de oppervlakte van een nagel.

Op de IEEE International Electron Devices-meeting hebben onderzoekers een geheel nieuwe chemische etstechniek gepresenteerd onder de naam Thermal Atomic Level Etching (Thermal ALE ), waarmee halfgeleiders op atomaire schaal kunnen worden bewerkt. Daarmee zijn 3D-transistors met een breedte van maar 2,5 nm te fabriceren, die ook nog eens weinig energie nodig hebben.

Er zijn al wel „atomaire“ etstechnieken, maar dit nieuwe proces is nauwkeurig en levert betere transistors op. Verder worden gangbare fabricagetechnieken voor het opdampen van atoomlagen op substraten gebruikt, wat de nieuwe techniek gemakkelijk te integreren maakt in bestaande fabricagetechnieken.

Atoom voor atoom

Bij deze microfabricagemethode wordt gebruik gemaakt van het op een substraat opdampen en etsen van de oppervlakte. Zoals gebruikelijk worden optische belichtingen en chemische etstechniek ingezet voor het vormen van de structuren. De modernste technieken zijn opdampen van atoomlagen (ALD) en etsen van atoomlagen ( ALE ). Bij ALD worden twee chemicaliën opgebracht op de oppervlakte van het substraat en die reageren in een vacuümreactor atoomlaag voor atoomlaag met elkaar tot een laag van de gewenste dikte is gevormd. Normaal gesproken wordt bij ALE gebruik gemaakt van hoogenergetisch plasma met ionen, die individuele atomen verwijderen. Bij dit proces ontstaan beschadigingen aan de oppervlakte als bijwerking. Bovendien wordt het materiaal blootgesteld aan de lucht, wat nog meer defecten veroorzaakt door oxidatie.Termisch ALE , zoals de University of Colorado het toepast, werkt met een chemische reactie die „ligandenuitwisseling“ wordt genoemd. Bij dit proces wordt een ion vervangen door een ligande van een andere verbinding. Bij het verwijderen van de chemicaliën worden met de liganden individuele atomen van de oppervlakte meeverwijderd. Tot nu toe werd deze techniek alleen gebruikt bij het etsen van oxiden.

De onderzoekers hebben thermisch ALE gemodificeerd voor halfgeleidermateriaal en werken met dezelfde reactor, die tot nu toe gereserveerd was voor ALD. Er is gebruik gemaakt van het gelegeerde halfgeleidermateriaal InGaAs (indium-gallium-arsenide), dat meer en meer wordt beschouwd als een beter alternatief voor silicium. Met fluorwaterstof wordt een laag metaalfluoride-moleculen gevormd op de oppervlakte. Dan wordt het materiaal bevochtigd met DMAC (dimethylaluminiumchloride). Bij het verwijderen van het DMAC worden individuele atomen meeverwijderd. Dit wordt honderden cycli lang herhaaldelijk gedaan. In een aparte reactor plaatsen de onderzoekers dan de gates van de transistoren.

Bij experimenten waren zo lagen van maar 0,02 nm dik te verwijderen zoals bij het afpellen van een ui. Dat maakt een enorm nauwkeurig etsproces mogelijk. En omdat deze techniek lijkt op die van ALD, kunnen hij plaatsvinden in dezelfde reactor die wordt gebruikt voor de depositie.

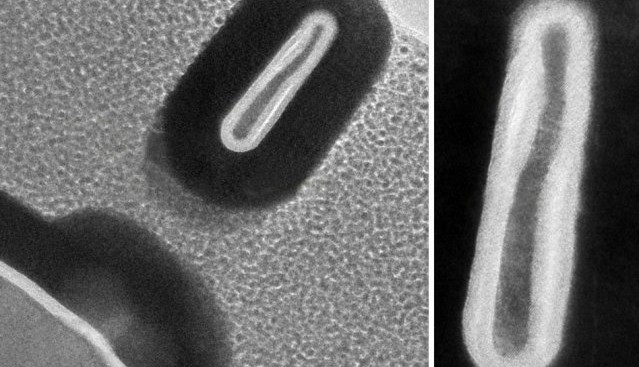

Dunnere fins

Met deze techniek zijn bijzonder kleine 3D-transistors te maken in de vorm van FinFET’s. FinFET’ s bestaan uit een dunne „vin“ van silicium die rechtop op het substraat staat. De gate zit in feite aan de zijkanten. Er zijn op die manier tussen de 7 en 30 miljard FinFET’s op een chip te realiseren. Sinds 2018 maken de leidende fabrikanten 7nm-FinFET’s. De meeste van de nieuwe FinFET’s hebben een breedte van 5 nm (de volgende drempelwaarde van de industrie) en een hoogte van ongeveer 220 nm. Bovendien wordt het materiaal beschermd door het vermijden van oxidatie.De nieuwe techniek levert een winst van ca. 60 % op in de transconductantie vergeleken met gewone FinFET’s. De transconductantie bepaalt hoeveel energie er nodig is aan de gate om de transistor te laten omschakelen.

Bron: MIT News

Read full article

Hide full article

Discussie (0 opmerking(en))