The Big Blue zegt: koperen interconnects zijn blijvertjes

29 november 2017

op

op

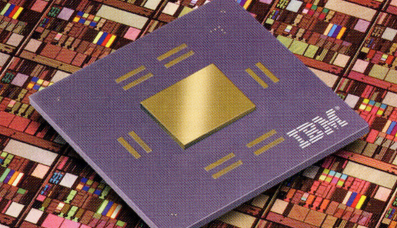

20 jaar nadat IBM, a.k.a. The Big Blue, als eerste begon met het gebruik van koperen interconnects bij de toen geruchtmakende 180nm-node voor CMOS-schakelingen, zijn er al veel andere materialen voorgesteld voor interconnects, zelfs grafeen. Ondanks dat zegt IBM dat het zal vasthouden aan koper omdat het, met kleine aanpassingen in de manier waarop het koper wordt gedeponeerd, de beste optie zal blijven zolang we CMOS blijven gebruiken.

"Grafeen is niet gemakkelijk te fabriceren en bovendien blijkt uit vergelijkingen dat grafeen niet uniform vloeit en niet de lage weerstanden van verbeterde koperen interconnects kan evenaren", verklaarde IBM Fellow Dan Edelstein onlangs tijdens een voordracht op het Nanotechnology Symposium. Hij legde uit: "koper met een dunne kobaltlaag geleidt de stroom beter dan grafeen en zelfs bij de kleinst denkbare afmetingen zijn koperen verbindingen nog steeds de beste oplossing, misschien in combinatie met een onderlaag van kobalt, nikkel, ruthenium of een ander edelmetaal uit de platinagroep.”

Sinds 1997 heeft IBM de twee belangrijkste bezwaren tegen koper overwonnen. Om te beginnen wordt gezegd dat koper het silicium aantast als het ermee in direct contact komt. Dat is opgelost door het koper in te kapselen in tantaalnitride en tantaal in een diffusielaag. En omdat het koper moest worden ingepakt in de tantaalverbinding, leek de populaire en gevestigde “substratieve” methode niet toepasbaar. Dat loste IBM op door gebruik te maken van een additieve methode met een soort elektrolytische depositie, zoals ook wordt gebruikt bij de fabricage van printplaten (PCB’s).

In het begin dacht men dat de technologie van koperen interconnects maar één generatie stand zou houden, maar inmiddels zijn we al 12 generaties verder. Bij The Big Blue zijn ze er vast van overtuigd dat dat voor CMOS zo zal blijven, misschien met uitzondering van de onderlaag bij geavanceerde siliciumtransistoren waar eventueel kobalt, nikkel, ruthenium of een ander edelmetaal uit de platinagroep nodig kan zijn.

Bron: EE Times

"Grafeen is niet gemakkelijk te fabriceren en bovendien blijkt uit vergelijkingen dat grafeen niet uniform vloeit en niet de lage weerstanden van verbeterde koperen interconnects kan evenaren", verklaarde IBM Fellow Dan Edelstein onlangs tijdens een voordracht op het Nanotechnology Symposium. Hij legde uit: "koper met een dunne kobaltlaag geleidt de stroom beter dan grafeen en zelfs bij de kleinst denkbare afmetingen zijn koperen verbindingen nog steeds de beste oplossing, misschien in combinatie met een onderlaag van kobalt, nikkel, ruthenium of een ander edelmetaal uit de platinagroep.”

Sinds 1997 heeft IBM de twee belangrijkste bezwaren tegen koper overwonnen. Om te beginnen wordt gezegd dat koper het silicium aantast als het ermee in direct contact komt. Dat is opgelost door het koper in te kapselen in tantaalnitride en tantaal in een diffusielaag. En omdat het koper moest worden ingepakt in de tantaalverbinding, leek de populaire en gevestigde “substratieve” methode niet toepasbaar. Dat loste IBM op door gebruik te maken van een additieve methode met een soort elektrolytische depositie, zoals ook wordt gebruikt bij de fabricage van printplaten (PCB’s).

In het begin dacht men dat de technologie van koperen interconnects maar één generatie stand zou houden, maar inmiddels zijn we al 12 generaties verder. Bij The Big Blue zijn ze er vast van overtuigd dat dat voor CMOS zo zal blijven, misschien met uitzondering van de onderlaag bij geavanceerde siliciumtransistoren waar eventueel kobalt, nikkel, ruthenium of een ander edelmetaal uit de platinagroep nodig kan zijn.

Bron: EE Times

Read full article

Hide full article

Discussie (0 opmerking(en))